Dear Readers,

There was an article published by SmartPlay Technologies back in 2015 when I was working with them. It has very useful information to understand the usage, advantages, and guidelines about System Verilog Assertions (SVA).

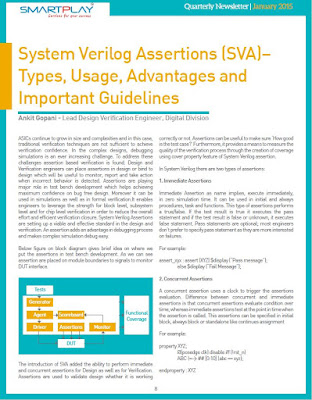

ASICs continue to grow in size and complexities and in this case, traditional verification techniques are not sufficient to achieve verification confidence. In complex designs, debugging simulations is an ever-increasing challenge. To address these challenges assertion-based verification is found. Design and Verification engineers can place assertions in design or bind to design which will be useful to monitor, report and take action when incorrect behavior is detected. Assertions are playing a major role in test bench development which helps to achieve maximum confidence on bug-free design. Moreover, it can be used in simulations as well as in formal verification. It enables engineers to leverage the strength for block level, subsystem level and for chip level verification in order to reduce the overall effort and efficient verification closure. System Verilog Assertions are setting up a viable and effective standard in design and verification. An assertion adds an advantage in the debugging process and makes complex simulation debug easy.

The introduction of SVA added the ability to perform immediate and concurrent assertions for Design as well as for Verification. Assertions are used to validate design whether it is working correctly or not. Assertions can be useful to make sure ‘How good is the test case?’ Furthermore, it provides a means to measure the quality of the verification process through the creation of coverage using cover property feature of System Verilog assertion.

Questions are

1. What type of System Verilog Assertions we have?

2. Where to put these assertions in our test bench development?

3. How to implement these assertions?

4. Usage, Advantage

5. What are the important Guidelines for SVA implementation?

To find more details please read this blog post "System Verilog Assertions (SVA) Types, Usage Advantages and Important Guidelines"

Thanks,

Ankit

Disclaimer

The content on this site is my own and not relates, in any way, to organizations I work for. Thank you, #ASICWithAnkit

My Blogs

Total Pageviews

Search This Blog

Feedback to 'ASIC With Ankit'

Please drop in the feedback to

asicwithankit@gmail.com

Followers

About Me

- Ankit Gopani

- SAN DIEGO, California, United States

- Working as a Lead Design Verification Engineer. As an ASIC Verification Engineer, we basically provide verification solutions to our customers for verifying their Intellectual Property and complex SoCs.The verification phase is divided into many forks like feasibility study for Specification and requirements, Design and Verification and finding bugs in Designs, review phase at each and every level. I pursued Diploma in E.C, B.E in Electronics and Communication and MBA in software project management. -ASIC With Ankit

ASIC With Ankit Blog Posts

- ASIC - Application Specific Integrated Circuits (4)

- ASIC Interview Question-Answers (2)

- ASIC Overview (1)

- Design Verification TestBench (1)

- EDA Tools (2)

- My Article published by popular websites (2)

- My Seminars-Sessions (1)

- Randomization; SystemVerilog (2)

- Recession Blast 2011-12 (1)

- Semiconductor Ecosystem (1)

- Semiconductor Industries (5)

- System Verilog - Verification (37)

- System Verilog - Coverage (1)

- System Veriog GOTHCA (2)

- Technology and Updates (5)

- Verilog-VHDL (2)

ASIC With Ankit

Labels

- ASIC - Application Specific Integrated Circuits (4)

- ASIC Interview Question-Answers (2)

- ASIC Overview (1)

- Design Verification TestBench (1)

- EDA Tools (2)

- My Article published by popular websites (2)

- My Seminars-Sessions (1)

- Randomization; SystemVerilog (2)

- Recession Blast 2011-12 (1)

- Semiconductor Ecosystem (1)

- Semiconductor Industries (5)

- System Verilog - Verification (37)

- System Verilog - Coverage (1)

- System Veriog GOTHCA (2)

- Technology and Updates (5)

- Verilog-VHDL (2)